# Synthesis and Verification Design Guide

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved. CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator, CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogicORE, LogicProfessor, MicroBlaze, MicroVia, MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, RocketIO, SelectIO, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex-II Pro, Virtex-II EasyPath, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devices and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owned and copyrighted by Xilinx. Copyright 1994-2003 Xilinx, Inc. All Rights Reserved. Except as stated herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

The following table shows the revision history for this document.

|          | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06/01/00 | 1.0     | Initial Xilinx® release.                                                                                                                                                                                                                                                                                                                                                                                |

| 06/15/00 | 1.1     | Accumulated miscellaneous updates and bug fixes.                                                                                                                                                                                                                                                                                                                                                        |

| 07/26/00 | 1.2     | Accumulated miscellaneous updates and bug fixes.                                                                                                                                                                                                                                                                                                                                                        |

| 08/28/00 | 1.3     | Fine tuning of text frame and paragraph format spacings.                                                                                                                                                                                                                                                                                                                                                |

| 04/11/01 | 2.0     | Revised formats to take advantage of FrameMaker 6.0 book features.                                                                                                                                                                                                                                                                                                                                      |

| 05/02/01 | 2.1     | Master page changes.                                                                                                                                                                                                                                                                                                                                                                                    |

| 07/11/01 | 2.2     | Accumulated miscellaneous updates and bug fixes.                                                                                                                                                                                                                                                                                                                                                        |

| 04/04/02 | 2.21    | Updated trademarks page in ug000_title.fm.                                                                                                                                                                                                                                                                                                                                                              |

| 06/24/02 | 3.0     | Initial Xilinx® release of corporate-wide common template set, used for User Guides, Tutorials, Release Notes, Manuals, and other lengthy, multiple-chapter documents created by both CMP and ITP. See related documents for further information.  *Descriptions for revisions prior to v3.0 have been abbreviated.* For a full summary of revision changes prior to v3.0, refer to v2.21 template set. |

| 06/06/03 | 4.0     | Name changed from Synthesis and Simulation Design Guide to Synthesis and Verification Design guide.                                                                                                                                                                                                                                                                                                     |

|          |         | Added new chapter for Equivalency Checking.                                                                                                                                                                                                                                                                                                                                                             |

|          |         | Accumulated miscellaneous updates and bug fixes.                                                                                                                                                                                                                                                                                                                                                        |

# **About This Guide**

This manual provides a general overview of designing Field Programmable Gate Arrays (FPGAs) with Hardware Description Languages (HDLs). It includes design hints for the novice HDL user, as well as for the experienced user who is designing FPGAs for the first time.

The design examples in this manual were created with Verilog and VHSIC Hardware Description Language (VHDL); compiled with various synthesis tools; and targeted for Spartan-II<sup>TM</sup>, Spartan-IIE<sup>TM</sup>, Spartan-3<sup>TM</sup>, Virtex<sup>TM</sup>, Virtex-E<sup>TM</sup>, Virtex-II<sup>TM</sup>, Virtex-II Pro<sup>TM</sup> and Virtex-II Pro X<sup>TM</sup> devices. Xilinx® equally endorses both Verilog and VHDL. VHDL may be more difficult to learn than Verilog and usually requires more explanation.

This manual does not address certain topics that are important when creating HDL designs, such as the design environment; verification techniques; constraining in the synthesis tool; test considerations; and system verification. Refer to your synthesis tool's reference manuals and design methodology notes for additional information.

Before using this manual, you should be familiar with the operations that are common to all Xilinx® software tools.

#### **Guide Contents**

This book contains the following chapters.

- Chapter 1, "Introduction," provides a general overview of designing Field Programmable Gate Arrays (FPGAs) with HDLs. This chapter also includes installation requirements and instructions.

- Chapter 2, "Understanding High-Density Design Flow," provides synthesis and Xilinx® implementation techniques to increase design performance and utilization.

- Chapter 3, "General HDL Coding Styles," includes HDL coding hints and design examples to help you develop an efficient coding style.

- Chapter 4, "Architecture Specific Coding Styles for Spartan™-II/-3,Virtex™/-E/-II/-II Pro/-II Pro X," includes coding techniques to help you use the latest Xilinx® devices.

- Chapter 5 "Virtex-II Pro™ Considerations," describes the special considerations encountered when simulating designs for Virtex-II Pro™ and Virtex-II Pro X™ FPGAs.

- Chapter 6, "Verifying Your Design," describes simulation methods for verifying the function and timing of your designs.

- Chapter 7, "Equivalency Checking," describes how to use third party tools to perform formal verification on your designs.

#### **Additional Resources**

For additional information, go to <a href="http://support.xilinx.com">http://support.xilinx.com</a>. The following table lists some of the resources you can access from this website. You can also directly access these resources using the provided URLs.

| Resource          | Description/URL                                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials         | Tutorials covering Xilinx® design flows, from design entry to verification and debugging                                                                                                                |

|                   | http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                                                           |

| Answer Browser    | Database of Xilinx® solution records                                                                                                                                                                    |

|                   | http://support.xilinx.com/xlnx/xil_ans_browser.jsp                                                                                                                                                      |

| Application Notes | Descriptions of device-specific design techniques and approaches                                                                                                                                        |

|                   | http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                              |

| Data Sheets       | Pages from The Programmable Logic Data Book, which contains device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging |

|                   | http://www.support.xilinx.com/xlnx/xweb/xil_publications_inde<br>x.jsp                                                                                                                                  |

| Problem Solvers   | Interactive tools that allow you to troubleshoot your design issues                                                                                                                                     |

|                   | http://support.xilinx.com/support/troubleshoot/psolvers.htm                                                                                                                                             |

| Tech Tips         | Latest news, design tips, and patch information for the Xilinx® design environment                                                                                                                      |

|                   | http://www.support.xilinx.com/xlnx/xil_tt_home.jsp                                                                                                                                                      |

#### **Conventions**

This document uses the following conventions. An example illustrates each convention.

# **Typographical**

The following typographical conventions are used in this document:

| Convention     | Meaning or Use                                                | Example              |

|----------------|---------------------------------------------------------------|----------------------|

| Courier font   | Messages, prompts, and program files that the system displays | speed grade: - 100   |

| Courier bold   | Literal commands that you enter in a syntactical statement    | ngdbuild design_name |

| Helvetica bold | Commands that you select from a menu                          | File → Open          |

|                | Keyboard shortcuts                                            | Ctrl+C               |

| Convention          | Meaning or Use                                                                                       | Example                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                     | Variables in a syntax<br>statement for which you must<br>supply values                               | ngdbuild design_name                                                                               |

| Italic font         | References to other manuals                                                                          | See the <i>Development System Reference Guide</i> for more information.                            |

|                     | Emphasis in text                                                                                     | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |

| Square brackets []  | An optional entry or parameter. However, in bus specifications, such as bus[7:0], they are required. | ngdbuild [option_name] design_name                                                                 |

| Braces { }          | A list of items from which you must choose one or more                                               | lowpwr ={on off}                                                                                   |

| Vertical bar        | Separates items in a list of choices                                                                 | lowpwr ={on off}                                                                                   |

| Vertical ellipsis   | Repetitive material that has been omitted                                                            | IOB #1: Name = QOUT' IOB #2: Name = CLKIN'                                                         |

| Horizontal ellipsis | Repetitive material that has been omitted                                                            | allow block block_name loc1 loc2 locn;                                                             |

# Online Document

The following conventions are used in this document:

| Convention            | Meaning or Use                                                                                    | Example                                                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Blue text             | Cross-reference link to a location in the current file or in another file in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Using Synthesis<br>Tools" for details. |

| Red text              | Cross-reference link to a location in another document                                            | See Figure 2-5 in the Virtex-II Platform FPGA User Guide.                                                  |

| Blue, underlined text | Hyperlink to a website (URL)                                                                      | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed files.                |

# **Table of Contents**

| Preface: About This Guide                                     |

|---------------------------------------------------------------|

| Guide Contents                                                |

| Additional Resources                                          |

| Conventions                                                   |

| Typographical                                                 |

| Online Document                                               |

| Chapter 1: Introduction                                       |

| Architecture Support 1                                        |

| Overview of Hardware Description Languages                    |

| Advantages of Using HDLs to Design FPGAs                      |

| Designing FPGAs with HDLs 2                                   |

| Using Verilog                                                 |

| Using VHDL                                                    |

| Comparing ASICs and FPGAs                                     |

| Using Synthesis Tools                                         |

| Using FPGA System Features    2      Designing Hierarchy    2 |

| Specifying Speed Requirements                                 |

| Xilinx® Internet Websites                                     |

| Xilinx® World Wide Web Site                                   |

| Technical Support Website                                     |

| Technical and Applications Support Hotlines                   |

| Xilinx® FTP Site                                              |

| Vendor Support Sites 2                                        |

| Chantan O. Undanatan dina Hinh Danaitu Daaina Flaur           |

| Chapter 2: Understanding High-Density Design Flow             |

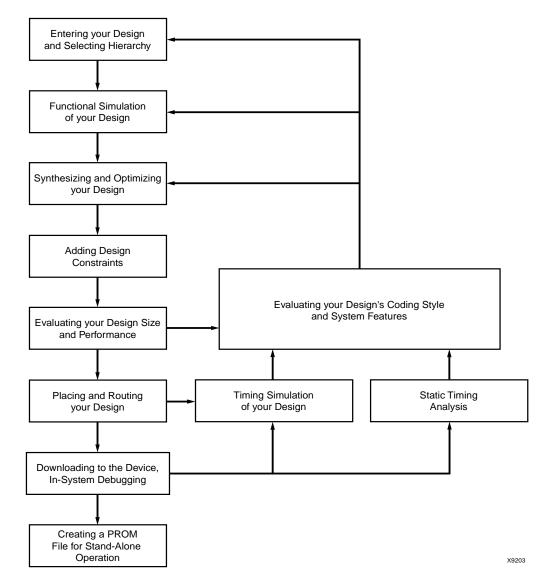

| Design Flow                                                   |

| Entering your Design and Selecting Hierarchy 2                |

| Design Entry Recommendations                                  |

| Using RTL Code                                                |

| Architecture Wizard                                           |

| Clocking Wizard                                               |

| RocketIO™ Wizard                                              |

| CORE Generator™                                               |

| Functional Simulation of your Design                          |

| Synthesizing and Optimizing your Design 2                     |

| Creating an Initialization File                               |

| Creating a Compile Run Script                                 |

| FPGA Compiler $II^{TM}$                                       |

| Synplify™                                                     |

| วว                                                                   |

|----------------------------------------------------------------------|

| 32                                                                   |

| 32                                                                   |

| 32                                                                   |

| 33                                                                   |

| 33                                                                   |

| 33                                                                   |

| 33                                                                   |

| 34                                                                   |

| 34                                                                   |

| 34                                                                   |

| 35                                                                   |

| 35                                                                   |

| 35                                                                   |

| 36                                                                   |

|                                                                      |

| 39                                                                   |

| 39                                                                   |

| 39                                                                   |

| 39                                                                   |

| 39                                                                   |

| <b>40</b>                                                            |

| 40                                                                   |

| 40                                                                   |

| 41                                                                   |

| 41                                                                   |

| 41                                                                   |

| 41                                                                   |

| 42                                                                   |

| 42                                                                   |

| 43                                                                   |

| 10                                                                   |

| 40                                                                   |

| 43                                                                   |

| 43<br>43                                                             |

|                                                                      |

|                                                                      |

|                                                                      |

| 43<br>45                                                             |

| 43<br>45<br>45                                                       |

| 43<br>45<br>46                                                       |

| 43<br>45<br>46<br>46                                                 |

| 43<br>45<br>46<br>46<br>46                                           |

| 43<br>45<br>46<br>46<br>47                                           |

| 43<br>45<br>46<br>46<br>47<br>48                                     |

| 43<br>45<br>46<br>46<br>47<br>48<br>48                               |

| 43<br>45<br>46<br>46<br>47<br>48<br>48<br>49                         |

| 43<br>45<br>46<br>46<br>47<br>48<br>48<br>49<br>50                   |

| 43<br>45<br>46<br>46<br>47<br>48<br>49<br>50<br>51                   |

| 43<br>45<br>46<br>46<br>47<br>48<br>49<br>50<br>51                   |

| 43<br>45<br>46<br>46<br>47<br>48<br>49<br>50<br>51<br>51             |

| 43<br>45<br>46<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>52       |

| 43<br>45<br>46<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>52<br>53 |

| 43<br>45<br>46<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>52       |

|                                                                      |

| Using Signals (VHDL)                                                                       |              |

|--------------------------------------------------------------------------------------------|--------------|

| Using Variables (VHDL)                                                                     | 56           |

| Coding for Synthesis                                                                       | 56           |

| Omit the Wait for XX ns Statement                                                          |              |

| Omit theAfter XX ns or Delay Statement                                                     |              |

| Omit Initial Values                                                                        |              |

| Order and Group Arithmetic Functions                                                       |              |

| Comparing If Statement and Case Statement                                                  |              |

| 4-to-1 Multiplexer Design with If Construct                                                |              |

| 4-to-1 Multiplexer Design with Case Construct                                              |              |

| Implementing Latches and Registers                                                         |              |

| D Latch Inference                                                                          |              |

| Converting D Latch to D Register                                                           | 64           |

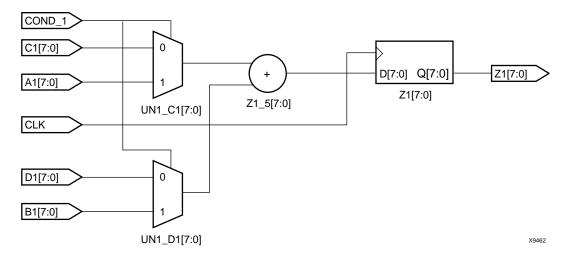

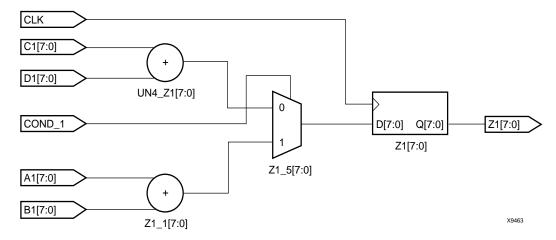

| Resource Sharing                                                                           | 65           |

| Reducing Gate Count                                                                        |              |

| Using Preset Pin or Clear Pin                                                              |              |

| Register Inference                                                                         |              |

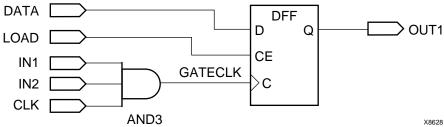

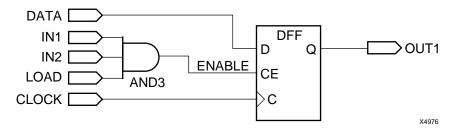

| Using Clock Enable Pin Instead of Gated Clocks                                             |              |

|                                                                                            |              |

| Chapter 4: Architecture Specific Coding Styles for S                                       | Spartan™-II/ |

| -3,Virtex™/-E/-II/-II Pro/-II Pro X                                                        | -            |

| -3, virtex/-E/-II/-II P10/-II P10 A                                                        |              |

| Introduction                                                                               | 75           |

| Instantiating Components                                                                   | 76           |

| Instantiating FPGA Primitives                                                              |              |

| Instantiating CORE Generator™ Modules                                                      |              |

| Using Boundary Scan (JTAG 1149.1)                                                          |              |

|                                                                                            |              |

| Using Global Clock Buffers                                                                 |              |

| Inserting Clock Buffers                                                                    |              |

|                                                                                            |              |

| Instantiating Buffers Driven from a Port                                                   |              |

|                                                                                            |              |

| Using Advanced Clock Management                                                            |              |

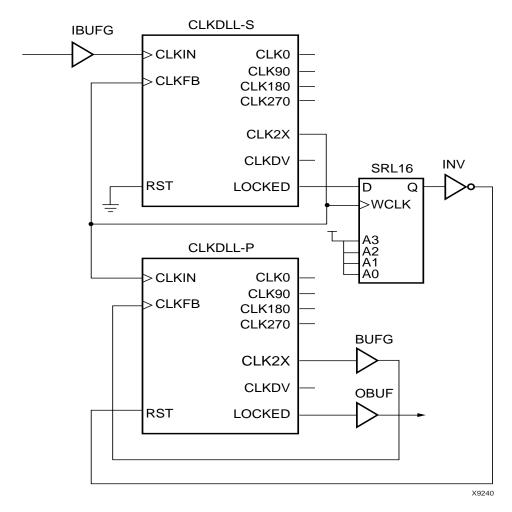

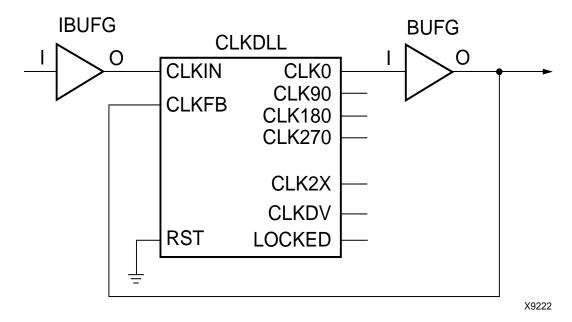

| Using CLKDLL (Virtex <sup>TM</sup> , Virtex-E <sup>TM</sup> and Spartan-II <sup>TM</sup> ) |              |

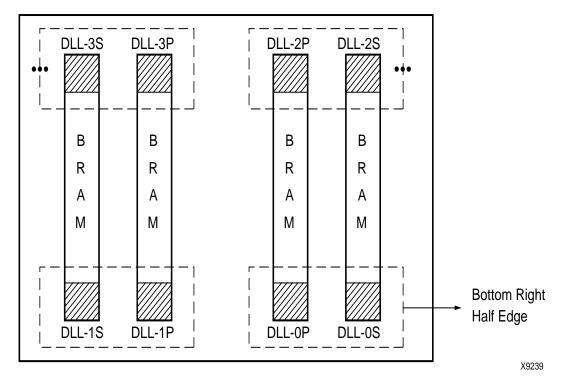

| Using the Additional CLKDLL in Virtex-E™                                                   |              |

| Using BUFGDLL                                                                              |              |

| CLKDLL Attributes                                                                          |              |

| Attaching Multiple Attributes to CLKDLL and DCM                                            |              |

| •                                                                                          |              |

| Using Dedicated Global Set/Reset Resource                                                  |              |

| Startup State                                                                              |              |

| Preset vs. Clear                                                                           |              |

| Implementing Inputs and Outputs                                                            |              |

| I/O Standards                                                                              |              |

| Inputs                                                                                     |              |

| Outputs                                                                                    |              |

| Using IOB Register and Latch                                                               |              |

| Using Dual Data Rate IOB Registers                                                         |              |

| Using Output Enable IOB Register                                                           |              |

| Using -pr Option with Map                                                                  |              |

| Virtex-E™ IOBs                                                                             |              |

| Additional I/O Standards                                                                   | 126          |

| Virtex™-II/II Pro/II Pro X, Spartan-3™ IOBs                                                        | 131 |

|----------------------------------------------------------------------------------------------------|-----|

| Differential Signaling in Virtex™-II/II Pro/II Pro X or Spartan-3™                                 | 131 |

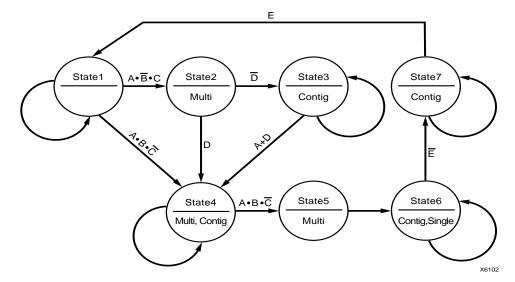

| Encoding State Machines                                                                            | 134 |

| Using Binary Encoding                                                                              |     |

| Binary Encoded State Machine VHDL Example                                                          |     |

| Binary Encoded State Machine Verilog Example                                                       |     |

| Using Enumerated Type Encoding                                                                     |     |

| Enumerated Type Encoded State Machine VHDL Example                                                 |     |

| Enumerated Type Encoded State Machine Verilog Example                                              |     |

| Using One-Hot Encoding                                                                             |     |

| One-hot Encoded State Machine VHDL Example                                                         |     |

| One-hot Encoded State Machine Verilog Example                                                      |     |

| Accelerating FPGA Macros with One-Hot Approach                                                     |     |

| Summary of Encoding Styles                                                                         |     |

| Initializing the State Machine                                                                     |     |

|                                                                                                    |     |

| Implementing Operators and Generate Modules                                                        |     |

| Adder and Subtractor                                                                               |     |

| Multiplier                                                                                         |     |

| Counters                                                                                           |     |

| Comparator                                                                                         |     |

| Encoder and Decoders                                                                               |     |

| LeonardoSpectrum™ Priority Encoding HDL Example                                                    |     |

| Implementing Memory                                                                                |     |

| Implementing Block RAM                                                                             |     |

| Instantiating Block SelectRAM™                                                                     | 154 |

| Instantiating Block SelectRAM™ in Virtex™-II/II Pro/II Pro X and                                   |     |

| Spartan-3™                                                                                         |     |

| Inferring Block SelectRAM™                                                                         |     |

| Implementing Distributed SelectRAM™                                                                |     |

| Implementing ROMs                                                                                  | 176 |

| RTL Description of a Distributed ROM VHDL Example                                                  |     |

| RTL Description of a Distributed ROM Verilog Example                                               | 177 |

| Implementing ROMs Using Block SelectRAM™                                                           | 178 |

| RTL Description of a ROM VHDL Example Using Block SelectRAM™                                       | 178 |

| RTL Description of a ROM Verilog Example using Block SelectRAM™                                    | 179 |

| Implementing FIFO                                                                                  | 180 |

| Implementing CAM                                                                                   | 180 |

| Using CORE Generator™ to Implement Memory                                                          | 181 |

| Implementing Shift Registers (Virtex <sup>™</sup> /E/II/II Pro/II Pro X and Spartan <sup>™</sup> - |     |

|                                                                                                    |     |

| Inferring SRL16 in VHDL                                                                            |     |

| Inferring SRL16 in Verilog                                                                         |     |

| Inferring Dynamic SRL16 in VHDL                                                                    |     |

| Inferring Dynamic SRL16 in Verilog                                                                 |     |

| Implementing LFSR                                                                                  |     |

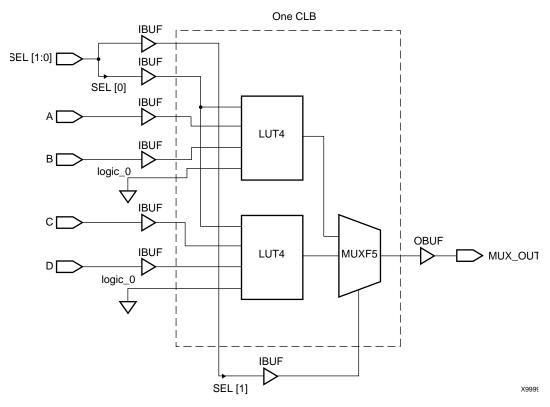

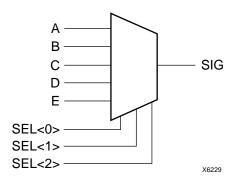

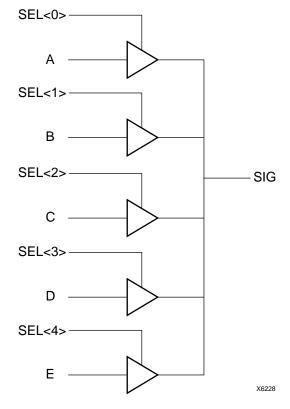

| Implementing Multiplexers                                                                          |     |

| Mux Implemented with Gates VHDL Example                                                            |     |

|                                                                                                    |     |

| Mux Implemented with Gates Verilog Example                                                         |     |

| Wide MUX Mapped to MUXFs                                                                           |     |

| Mux Implemented with BUFTs VHDL Example                                                            |     |

| Mux Implemented with BUFTs Verilog Example                                                         |     |

| Using Pipelining                                                                                   | 188 |

|              | ore Pipelining                                                              |     |

|--------------|-----------------------------------------------------------------------------|-----|

| Afte         | er Pipelining                                                               | 188 |

| Design       | Hierarchy                                                                   | 189 |

|              | ing Synthesis Tools with Hierarchical Designs                               |     |

|              | Restrict Shared Resources to Same Hierarchy Level                           |     |

|              | Compile Multiple Instances Together                                         |     |

|              | Restrict Related Combinatorial Logic to Same Hierarchy Level                |     |

|              | Separate Speed Critical Paths from Non-critical Paths                       |     |

|              | Restrict Combinatorial Logic that Drives a Register to Same Hierarchy Level |     |

|              | Restrict Module Size                                                        |     |

|              | Register All Outputs                                                        |     |

|              | Restrict One Clock to Each Module or to Entire Design                       |     |

| Chapter 5:   | Virtex-II Pro™ Considerations                                               |     |

| Introdu      | ction                                                                       | 191 |

|              | SmartModels to Simulate Virtex-II Pro <sup>TM</sup> Designs                 |     |

| _            |                                                                             |     |

|              | tion Components                                                             |     |

| Overvie      | ew of Virtex-II Pro™ Simulation Flow                                        | 192 |

| SmartM       | Iodels                                                                      | 193 |

| Suppor       | ted Simulators                                                              | 193 |

|              | aris®                                                                       |     |

| Wir          | ndows®                                                                      | 193 |

| Require      | ed Software                                                                 | 194 |

| -            | aris®                                                                       |     |

|              | ndows®                                                                      |     |

| Installi     | ng SmartModels from Xilinx® Implementation Tools                            | 194 |

|              | thod One                                                                    |     |

| 1,10,        | Windows®                                                                    |     |

|              | Solaris®.                                                                   |     |

| Met          | thod Two                                                                    |     |

|              | Solaris®                                                                    | 195 |

|              | Windows®                                                                    | 195 |

| Runnin       | g Simulation                                                                | 196 |

|              | I® ModelSim™ SE - Solaris®                                                  |     |

|              | Simulator Setup                                                             | 196 |

|              | Running Simulation                                                          |     |

| MT           | I® ModelSim™ SE - Windows®                                                  | 197 |

|              | Simulator Setup                                                             | 197 |

|              | Running Simulation                                                          |     |

| Cad          | lence® Verilog-XL™ - Solaris®                                               |     |

|              | Running Simulation                                                          |     |

| Cac          | lence® NC-Verilog™ - Solaris®                                               |     |

| 6            | Running Simulation                                                          |     |

| Syn          | opsys® VCS™ - Solaris®                                                      |     |

|              | Running Simulation                                                          | 2UZ |

| Chapter 6:   | Verifying Your Design                                                       |     |

| <del>-</del> | ction                                                                       | ეტი |

|              |                                                                             |     |

| Adherii      | ng to Industry Standards                                                    | 204 |

| <b>Simulation Points</b>                                                     | )5    |

|------------------------------------------------------------------------------|-------|

| Register Transfer Level (RTL)                                                |       |

| Post-Synthesis (Pre-NGDBuild) Gate-Level Simulation                          |       |

| Post-NGDBuild (Pre-Map) Gate-Level Simulation                                |       |

| Post-Map Partial Timing (CLB and IOB Block Delays)                           |       |

| Timing Simulation Post-Place and Route Full Timing (Block and Net Delays) 20 |       |

| Providing Stimulus                                                           |       |

| VHDL/Verilog Libraries and Models                                            |       |

| Locating Library Source Files                                                |       |

| Using the UNISIM Library                                                     |       |

| UNISIM Library Structure                                                     |       |

| Using the CORE Generator™ XilinxCoreLib Library                              |       |

| CORE Generator™ Library Structure                                            |       |

| Using the SIMPRIM Library                                                    |       |

| SIMPRIM Library Structure                                                    |       |

| Using the SmartModel Library <sup>TM</sup>                                   |       |

|                                                                              |       |

| Compiling Xilinx® Simulation Libraries (COMPXLIB)                            |       |

| Compiling Simulation Libraries                                               |       |

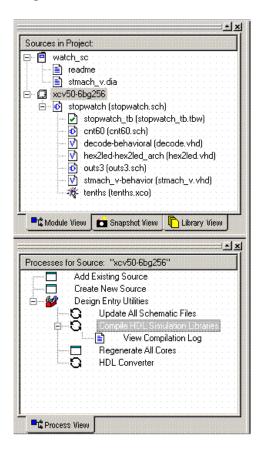

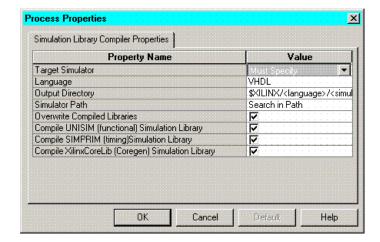

| From Project Navigator                                                       |       |

| From Command Line                                                            |       |

| Library Support                                                              |       |

| Device Family Support                                                        |       |

| Simulator Support                                                            |       |

| COMPXLIB Syntax                                                              |       |

| COMPXLIB Options                                                             |       |

| COMPXLIB Command Line Examples                                               |       |

| Specifying Run Time Options                                                  |       |

| Sample Configuration File:                                                   |       |

| Running NetGen                                                               | :1    |

| Creating a Simulation Netlist                                                |       |

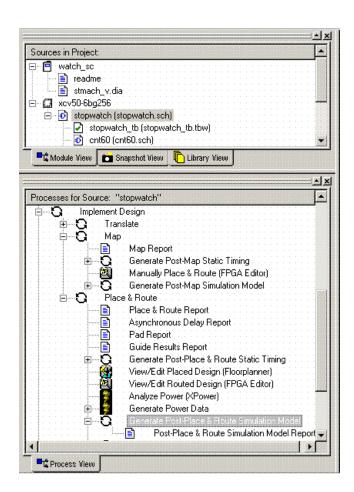

| From Project Navigator                                                       |       |

| From XFLOW                                                                   |       |

| From Command Line or Script File                                             |       |

| Disabling 'X' Propagation                                                    |       |

| Using the ASYNC_REG Attribute                                                |       |

| Using Global Switches                                                        |       |

| Use With Care                                                                |       |

| MIN/TYP/MAX Simulation                                                       |       |

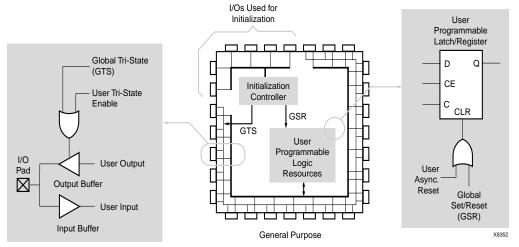

| <b>Understanding the Global Reset and Tristate for Simulation</b>            | 0     |

| <b>Simulating VHDL</b>                                                       | 31    |

| Emulating the Global GSR pulse in VHDL in Functional Simulation              | 31    |

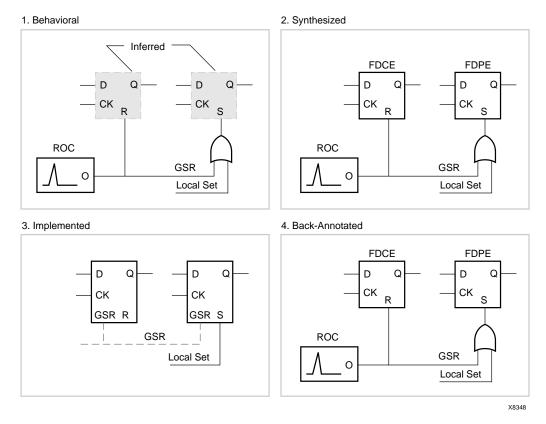

| Using VHDL Reset-On-Configuration (ROC) Cell                                 | 31    |

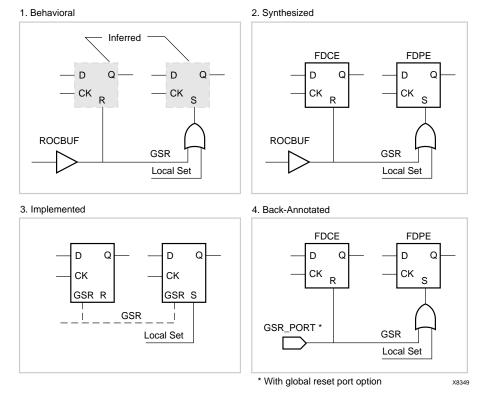

| Using VHDL ROCBUF Cell                                                       |       |

| Using VHDL STARTBUF_VIRTEX, STARTBUF_VIRTEX2 Block or the STARTBUF_SPA       | RTAN2 |

| Block                                                                        |       |

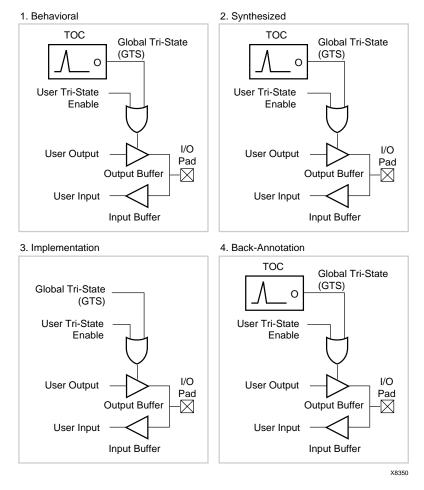

| Emulating the Global GTS pulse in a VHDL Functional Simulation               |       |

| Using VHDL Tristate-On-Configuration (TOC)                                   |       |

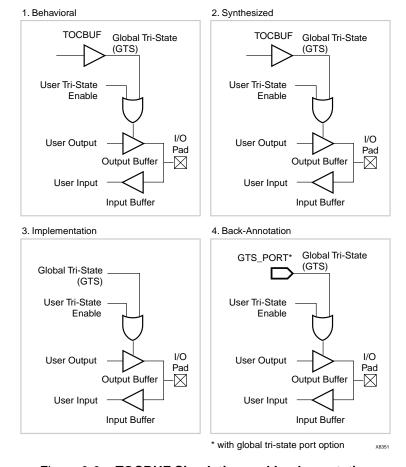

| Using VHDL TOCBUF                                                            |       |

| Using VHDL STARTBUF_VIRTEX, STARTBUF_VIRTEX2 or STARTBUF_SPARTAN2 B          |       |

|                                                                              |       |

| STARTBUF_VIRTEX Model Example                                                |       |

| Simulating Special Components in VHDL                                        | 4     |

| Simulating CORE Generator™ Components in VHDL               |            |

|-------------------------------------------------------------|------------|

| Boundary Scan and Readback                                  | 244        |

| Generics Support Considerations                             | 244        |

| Differential I/O (LVDS, LVPECL)                             | 245        |

| Simulating a LUT                                            |            |

| Simulating Virtex™ Block SelectRAM™                         | 246        |

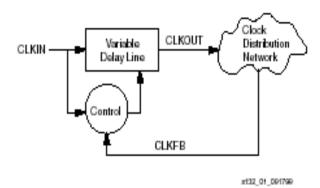

| Simulating the Virtex™ Clock DLL                            |            |

| Simulating the Virtex™-II/II Pro/II Pro X/Spartan-3™ DCM    | 249        |

| Simulating SRLs                                             | 252        |

| Simulating Verilog                                          | 253        |

| Defining Global Signals in Verilog                          |            |

| Using the glbl.v Module                                     |            |

| Defining GSR/GTS in a Test Bench                            |            |

| Emulating the Global GSR in a Verilog Functional Simulation |            |

| Simulating Special Components in Verilog                    |            |

| Boundary Scan and Readback                                  |            |

| Defparam Support Considerations                             |            |

| Differential I/O (LVDS, LVPECL)                             |            |

| LUT                                                         |            |

| SRL16                                                       |            |

| Block RAM                                                   |            |

| CLKDLL                                                      |            |

| DCM                                                         |            |

| Simulation CORE Generator™ Components                       |            |

| Design Hierarchy and Simulation                             |            |

| RTL Simulation Using Xilinx® Libraries                      |            |

| · · · · · · · · · · · · · · · · · · ·                       |            |

| Timing Simulation                                           |            |

| Glitches in your Design                                     |            |

| CLKDLL/DCM Clocks do not appear de-skewed                   |            |

| Simulating the DLL/DCM                                      |            |

| TRACE/Simulation Model Differences                          |            |

| Non-LVTTL Input Drivers                                     |            |

| Viewer Considerations                                       |            |

| Attributes for Simulation and Implementation                |            |

| Simulating the DCM in Digital Frequency Synthesis Mode Only |            |

| Debugging Timing Problems                                   |            |

| Identifying Timing Violations                               |            |

| Verilog System Timing Tasks                                 |            |

| VITAL Timing Checks                                         |            |

| Timing Problem Root Causes                                  |            |

| Design Not Constrained                                      |            |

| Path Not or Improperly Constrained                          |            |

| Design Does Not Meet Timespec                               |            |

| Simulation Clock Does Not Meet Timespec                     |            |

| Unaccounted Clock Skew                                      | 269        |

| Asynchronous Inputs, Asynchronous Clock Domains,            | 000        |

| Crossing Out-of-Phase                                       |            |

| Debugging Tips                                              |            |

| Special Considerations for Setup and Hold Violations        |            |

| Zero Hold Time Considerations                               |            |

| Negative Hold Times                                         | 271<br>271 |

| RAM Considerations                                          | 7/1        |

| Hierarchy Considerations                                                     |                |

|------------------------------------------------------------------------------|----------------|

| \$Width Violations                                                           |                |

| \$Recovery Violations                                                        | . 272          |

| Simulation Flows                                                             | . 273          |

| ModelSim™ Vcom                                                               |                |

| Using Shared Precompiled Libraries                                           |                |

| Scirocco <sup>TM</sup>                                                       |                |

| Using Shared Precompiled Libraries                                           | . 273          |

| NC-VHDL <sup>TM</sup>                                                        | . 274          |

| Using Shared Precompiled Libraries                                           |                |

| NC-Verilog™                                                                  |                |

| Using Library Source Files With Compile Time Options                         | . 275          |

| Using Shared Precompiled Libraries                                           |                |

| VCS <sup>TM</sup> /VCSi <sup>TM</sup>                                        | . 276          |

| Using Library Source Files With Compile Time Options                         | . 276          |

| Using Shared Precompiled Libraries                                           | . 277          |

| ModelSim™ Vlog                                                               |                |

| Using Library Source Files With Compile Time Options                         |                |

| Using Shared Precompiled Libraries                                           |                |

| IBIS                                                                         | . 279          |

| STAMP                                                                        |                |

| STAINIF                                                                      | . 200          |

| Objected 7. Equivalency Objection                                            |                |

| Chapter 7: Equivalency Checking                                              |                |

| Introduction                                                                 | . 281          |

| Software and Device Support                                                  | . 281          |

| Supported Equivalency Checking Software                                      |                |

| Supported Synthesis Tools                                                    |                |

| Supported Devices                                                            |                |

|                                                                              |                |

| Equivalency Checking Compatible Simulation Models                            |                |

| Setup for Synopsys® Formality™ and Verplex® Conformal™ FPGA                  |                |

| Setup for Synopsys® Formality™                                               |                |

| Setup for Verplex® Conformal™ FPGA                                           | . 283          |

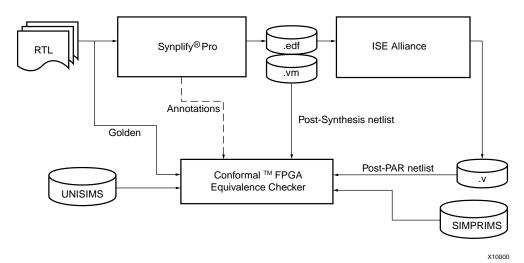

| Conformal™ FPGA and Synplify Pro™ Flow                                       | . 283          |

| RTL vs. Post-Synthesis                                                       | . 284          |

| Turning on Verification Mode                                                 |                |

| Running the DO File in Conformal™ FPGA                                       |                |

| Using CORE Generator™ Components with Conformal RTL vs. Post-Synthesis Veri  |                |

|                                                                              |                |

| Black Boxing Entire Modules                                                  |                |

| Post-Synthesis vs. Post-Place and Route                                      |                |

| Implementing the Design and Running NetGen                                   |                |

| Creating a DO File to Run Conformal Post-Synthesis vs. Post-PAR Verification |                |

| Running the DO File in Conformal™ FPGA                                       |                |

| Using CORE Generator™ Components with Conformal Post-Synthesis vs. Post-PAI  |                |

| Verification                                                                 |                |

| Black Boxing Entire Modules                                                  |                |

| Known Issues                                                                 |                |

|                                                                              |                |

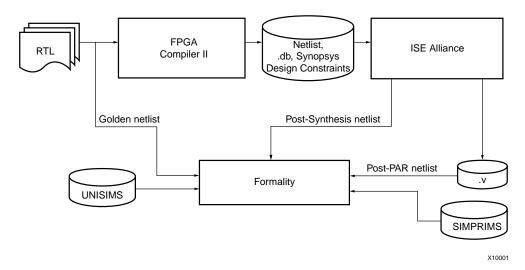

| Formality <sup>TM</sup> and FPGA Compiler II <sup>TM</sup> Flow              | . 289          |

| RTL vs. Post-Synthesis                                                       |                |

| v                                                                            | . 289          |

| Synthesizing the Design                                                      | . 289<br>. 289 |

| Creating a Script File to Run Formality™ for RTL vs. Post-Synthesis Verification 2 | 290   |

|------------------------------------------------------------------------------------|-------|

| Running the Script in Formality™                                                   | 291   |

| Using CORE Generator™ Components with Formality™ RTL vs.                           |       |

| Post-Synthesis Verification 2                                                      | 291   |

| RTL to Post-Place and Route                                                        | 292   |

| Implementing the Design and Running NetGen                                         | 292   |

| Creating a Script File to Run RTL vs. Post-PAR Verification                        |       |

| Running the Script in Formality™                                                   |       |

| Using CORE Generator™ Components with Formality™ RTL vs. Post-PAR Verification     |       |

|                                                                                    |       |

| Known Issues                                                                       |       |

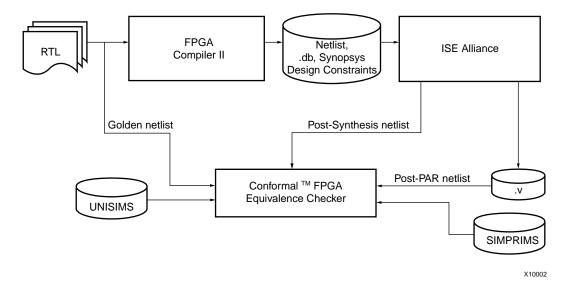

| Conformal™ FPGA and FPGA Compiler II™ Flow                                         | 294   |

| RTL vs. Post-Synthesis                                                             | 295   |

| Synthesizing the Design                                                            | 295   |

| Generating a Post-NGDBuild Netlist                                                 |       |

| Creating a DO File to Run RTL vs. Post-Synthesis Verification                      | 295   |

| Running the DO File in Conformal™ FPGA                                             | 296   |

| Using CORE Generator™ Components with Conformal RTL vs. Post-Synthesis Verifica    | ation |

|                                                                                    |       |

| RTL to Post-Place and Route                                                        | 297   |

| Implementing the Design and Running NetGen                                         | 297   |

| Creating a DO File to Run RTL vs. Post-PAR Verification                            |       |

| Running the DO File in Conformal™ FPGA                                             |       |

| Using CORE Generator™ Components with Conformal RTL vs. Post-PAR Verification      |       |

| ·                                                                                  | 299   |

# Introduction

This chapter provides a general overview of designing Field Programmable Gate Arrays (FPGAs) with HDLs, and also includes installation requirements and instructions. It includes the following sections.

- "Architecture Support"

- "Overview of Hardware Description Languages"

- "Advantages of Using HDLs to Design FPGAs"

- "Designing FPGAs with HDLs"

- "Xilinx® Internet Websites"

- "Vendor Support Sites"

# **Architecture Support**

The software supports the following architecture families in this release.

- Virtex<sup>TM</sup>-II/-E

- Virtex<sup>™</sup>-II PRO and Virtex<sup>™</sup>-II PRO X

- Spartan<sup>™</sup>-II/-IIE/-3

- CoolRunner<sup>™</sup> XPLA3/-II/-IIS

- XC9500<sup>™</sup>/XL/XV

# **Overview of Hardware Description Languages**

Hardware Description Languages (HDLs) are used to describe the behavior and structure of system and circuit designs. This chapter includes a general overview of designing FPGAs with HDLs. HDL design examples are provided in subsequent chapters of this book, and design examples can be downloaded from the Xilinx® website. System requirements and installation instructions for designs available from the web are also provided in this chapter.

This chapter also includes a brief description of why using FPGAs is more advantageous than using ASICs for your design needs.

To learn more about designing FPGAs with HDLs, Xilinx® recommends that you enroll in the appropriate training classes offered by Xilinx® and by the vendors of synthesis software. An understanding of FPGA architecture allows you to create HDL code that effectively uses FPGA system features.

For the latest information on Xilinx® parts and software, visit the Xilinx® website at <a href="http://www.xilinx.com">http://www.xilinx.com</a>. On the Xilinx® home page, click on Products. You can get

answers to your technical questions from the Xilinx® support website at <a href="http://www.support.xilinx.com">http://www.support.xilinx.com</a>. On the support home page, click on Advanced Search to set up search criteria that match your technical questions. You can also download software service packs from from this website. On the support home page, click on Software, and then Service Packs. Software documentation, tutorials, and design files are also available from this website.

# **Advantages of Using HDLs to Design FPGAs**

Using HDLs to design high-density FPGAs is advantageous for the following reasons.

- Top-Down Approach for Large Projects—HDLs are used to create complex designs. The top-down approach to system design supported by HDLs is advantageous for large projects that require many designers working together. After the overall design plan is determined, designers can work independently on separate sections of the code.

- Functional Simulation Early in the Design Flow—You can verify the functionality of your

design early in the design flow by simulating the HDL description. Testing your

design decisions before the design is implemented at the RTL or gate level allows you

to make any necessary changes early in the design process.

- Synthesis of HDL Code to Gates—You can synthesize your hardware description to a

design implemented with gates. This step decreases design time by eliminating the

need to define every gate. Synthesis to gates also reduces the number of errors that

can occur during a manual translation of a hardware description to a schematic

design. Additionally, you can apply the automation techniques used by the synthesis

tool (such as machine encoding styles or automatic I/O insertion) during the

optimization of your design to the original HDL code, resulting in greater efficiency.

- Early Testing of Various Design Implementations—HDLs allow you to test different implementations of your design early in the design flow. You can then use the synthesis tool to perform the logic synthesis and optimization into gates. Additionally, Xilinx® FPGAs allow you to implement your design at your computer. Since the synthesis time is short, you have more time to explore different architectural possibilities at the Register Transfer Level (RTL). You can reprogram Xilinx® FPGAs to test several implementations of your design.

- Reuse of RTL Code You can retarget RTL code to new FPGA architectures with a minimum of recoding.

# **Designing FPGAs with HDLs**

If you are more familiar with schematic design entry, you may find it difficult at first to create HDL designs. You must make the transition from graphical concepts, such as block diagrams, state machines, flow diagrams, and truth tables, to abstract representations of design components. You can ease this transition by not losing sight of your overall design plan as you code in HDL. To effectively use an HDL, you must understand the syntax of the language; the synthesis and simulator software; the architecture of your target device; and the implementation tools. This section gives you some design hints to help you create FPGAs with HDLs.

# Using Verilog

Verilog® is popular for synthesis designs because it is less verbose than traditional VHDL, and it is standardized as IEEE-STD-1364-95. It was not originally intended as an input to synthesis, and many Verilog constructs are not supported by synthesis software. The

www.xilinx.com

1-800-255-7778

Verilog examples in this manual were tested and synthesized with current, commonlyused FPGA synthesis software. The coding strategies presented in the remaining chapters of this manual can help you create HDL descriptions that can be synthesized.

#### **Using VHDL**

VHSIC Hardware Description Language (VHDL) is a hardware description language for designing Integrated Circuits (ICs). It was not originally intended as an input to synthesis, and many VHDL constructs are not supported by synthesis software. However, the high level of abstraction of VHDL makes it easy to describe the system-level components and testbenches that are not synthesized. In addition, the various synthesis tools use different subsets of the VHDL language. The examples in this manual will work with most commonly used FPGA synthesis software. The coding strategies presented in the remaining chapters of this manual can help you create HDL descriptions that can be synthesized.

#### Comparing ASICs and FPGAs

Xilinx® FPGAs are reprogrammable and when combined with an HDL design flow can greatly reduce the design and verification cycle seen with traditional ASICs.

#### Using Synthesis Tools

Most of the commonly-used FPGA synthesis tools have special optimization algorithms for Xilinx® FPGAs. Constraints and compiling options perform differently depending on the target device. There are some commands and constraints in ASIC synthesis tools that do not apply to FPGAs and, if used, may adversely impact your results. You should understand how your synthesis tool processes designs before creating FPGA designs. Most FPGA synthesis vendors include information in their manuals specifically for Xilinx® FPGAs.

# Using FPGA System Features

You can improve device performance and area utilization by creating HDL code that uses FPGA system features, such as global reset, wide I/O decoders, and memory. FPGA system features are described in this manual.

#### **Designing Hierarchy**

Current HDL design methods are specifically written for ASIC designs. You can use some of these ASIC design methods when designing FPGAs; however, certain techniques may unnecessarily increase the number of gates or CLB levels. This design guide will train you in techniques for optional FPGA design methodologies.

Design hierarchy is important in the implementation of an FPGA and also during incremental or interactive changes. Some synthesizers maintain the hierarchical boundaries unless you group modules together. Modules should have registered outputs so their boundaries are not an impediment to optimization. Otherwise, modules should be as large as possible within the limitations of your synthesis tool. The "5,000 gates per module" rule is no longer valid, and can interfere with optimization. Check with your synthesis vendor for the current recommendations for preferred module size. As a last resort, use the grouping commands of your synthesizer, if available. The size and content

of the modules influence synthesis results and design implementation. This manual describes how to create effective design hierarchy.

### Specifying Speed Requirements

To meet timing requirements, you should understand how to set timing constraints in both the synthesis and placement/routing tools. For more information, see "Setting Constraints" in Chapter 2.

#### Xilinx® Internet Websites

You can get product information and product support from the Xilinx® internet websites. Both sites are described in the following sections.

#### Xilinx® World Wide Web Site

You can reach the Xilinx® website at <a href="http://www.xilinx.com">http://www.xilinx.com</a> The following features can be accessed from the Xilinx® website.

- Products You can find information about new Xilinx® products that are being offered, as well as previously announced Xilinx® products.

- *Service and Support* You can jump to the Xilinx® technical support site by choosing Service and Support.

- Xpresso Cafe —You can purchase Xilinx® software, hardware and software tool

education classes through Xilinx® and Xilinx distributors.

#### **Technical Support Website**

Answers to questions, tutorials, Application notes, software manuals and information on using Xilinx® products can be found on the technical support website. You can reach the support website at <a href="http://www.support.xilinx.com">http://www.support.xilinx.com</a>. The following features can be accessed from the Xilinx® support website.

- Troubleshoot You can do an advanced search on the <u>Answers Database</u> to troubleshoot questions or issues you have with your design.

- Software You can download the latest software service packs, IP updates, and product information from the <u>Xilinx Support Website</u>.

- Library You can view the Software manuals from this website. The manuals are

provided in both HTML, viewable through most HTML browsers, and PDF. The

Databook, CORE Generator™ documentation and data sheets are also available.

- Design You can find helpful application notes that illustrate specific design solutions and methodologies.

- Services You can open a support case when you need to have information from a Xilinx® technical support person. You can also find information about your hardware or software order.

- Feedback —We are always interested in how well we're serving our customers. You can

let us know by filling out our customer service survey questionnaire.

You can contact Xilinx® technical support and application support for additional information and assistance in the following ways.

### **Technical and Applications Support Hotlines**

The telephone hotlines give you direct access to Xilinx Application Engineers worldwide. You can also e-mail or fax your technical questions to the same locations.

Table 1-1: Technical Support

| Location                 | Telephone                             | Electronic Mail                                                                  | Support Hours                              |

|--------------------------|---------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------|

| North America            | +1 800 255 7778 or<br>+1 408 879 5199 | link to http://support.xilinx.com/ support/clearexpress/ websupport.htm          | M,T,W, F 7:00-5:00 PST<br>Th 7:00-4:00 PST |

| United Kingdom           | +44-870-7350-610                      | link to http://support.xilinx.com/ support/clearexpress/ websupport.htm          | M-F 8:00 -5:30 GMT                         |

| France                   | +33-1-3463-0100                       | link to<br>http://support.xilinx.com/<br>support/clearexpress/<br>websupport.htm | M-F 8:00 -5:30 GMT                         |

| Germany                  | +49- 180-3-60-60-60                   | link to http://support.xilinx.com/ support/clearexpress/ websupport.htm          | M-F 8:00 -5:30 GMT                         |

| <sup>a</sup> Sweden      | +46- 8-33-14-00                       | link to<br>http://support.xilinx.com/<br>support/clearexpress/<br>websupport.htm | M-F 8:00 -5:30 GMT                         |

| <sup>a</sup> Netherlands | +31 (0)800 0233868                    | link to http://support.xilinx.com/ support/clearexpress/ websupport.htm          | M-F 8:00 -5:30 GMT                         |

| <sup>a</sup> Belgium     | +32 (0)800 90913                      | link to http://support.xilinx.com/ support/clearexpress/ websupport.htm          | M-F 8:00 -5:30 GMT                         |

| Rest of Europe           | +44 870 7350-610                      | link to<br>http://support.xilinx.com/<br>support/clearexpress/<br>websupport.htm | M-F 8:00 -5:30 GMT                         |

| Japan                    | +81 3 5321 7750                       | link to http://support.xilinx.com/ support/clearexpress/ websupport.htm          | M-F 9:00 -12:00,<br>1:00-5:00 JST          |

| Hong Kong                | +852 2 424 5200                       | china_support@xilinx.com                                                         |                                            |

| Taiwan                   | +886 2 2174 1388                      | taiwan_support@xilinx.com                                                        |                                            |

| China                    | +852 2 424 5200                       | china_support@xilinx.com                                                         |                                            |

Table 1-1: Technical Support

| Location                  | Telephone       | Electronic Mail                                                         | Support Hours |

|---------------------------|-----------------|-------------------------------------------------------------------------|---------------|

| <sup>a</sup> Rest of Asia | +1 408 879 5199 | link to http://support.xilinx.com/ support/clearexpress/ websupport.htm |               |

| Corporate<br>Switchboard  | 1-408-559-7778  | link to http://support.xilinx.com/ support/clearexpress/ websupport.htm |               |

a. English language support

**Note:** When e-mailing or faxing inquiries, provide your complete name, company name, and phone number. Also, provide a complete problem description including your design entry software and design stage.

#### Xilinx® FTP Site

#### ftp://ftp.xilinx.com

The FTP site provides online access to automated tutorials, design examples, online documents, utilities, and published patches.

# **Vendor Support Sites**

Vendor support for synthesis and verification products can be obtained at the following locations.

Table 1-2: Vendor Support Sites

| Vendor Name              | Telephone      | Electronic Mail             | Website                |

|--------------------------|----------------|-----------------------------|------------------------|

| Synopsys®                | 1-800-245-8005 | support_center@synopsys.com | www.synopsys.com       |

| Cadence®-Concept-<br>HDL | 1-877-237-4911 | support@cadence.com         | sourcelink.cadence.com |

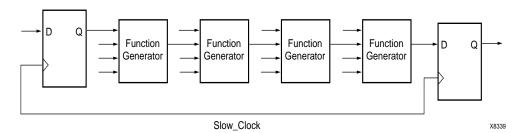

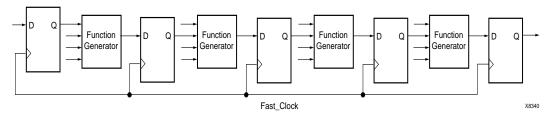

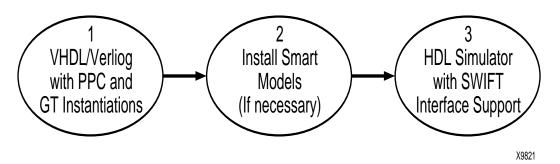

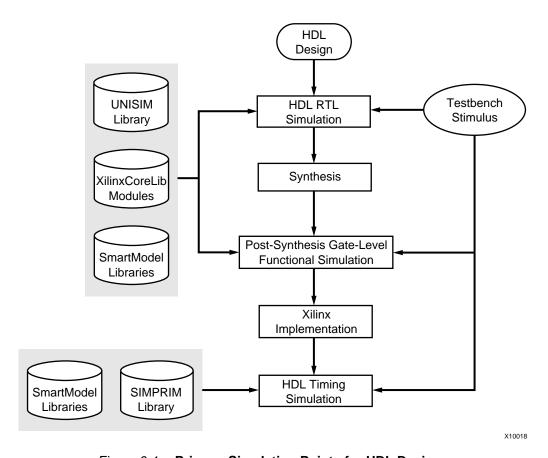

| Mentor Graphics®         | 1-800-547-4303 | support_net@mentor.com      | www.mentor.com         |